- Home >

- Artifacts of IP Heritage >

- 2011 >

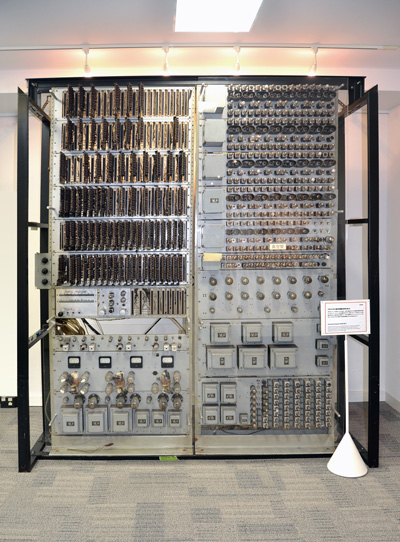

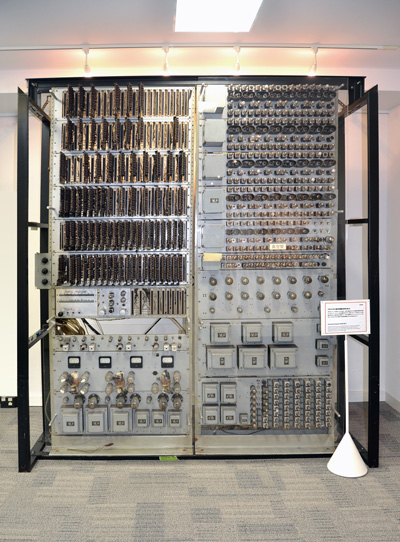

- HIPAC MK-1

HIPAC MK-1

| Manufactured in | 1957 |

|---|---|

| Manufactured by | Hitachi, Ltd. |

| Owner | Hitachi, Ltd. |

| Location of historical materials | Hitachi, Ltd., 1-280, Higashi-koigakubo, Kokubunji-shi, Tokyo, 185-8601 Japan |

| Visitor information | Not open to the public (Ask for a visit) |

| Contact | Hitachi, Ltd., Central Research Laboratory, Tel.+81-42-323-1111 |

HIPAC MK-1, developed by the Central Research Laboratory, Hitachi, Ltd. in 1957, is a digital computer with a stored program. The parametron device invented in 1954 at the University of Tokyo was used as the arithmetic element in HIPAC MK-1 and a magnetic drum was used for the memory unit.

HIPAC MK-1 was designed with reference to the EDSAC built by the University of Cambridge and the ILLIAC built by the University of Illinois. Approximately 4000 parametron devices were used in HIPAC MK-1, and with a clock frequency of 10 kHz, calculation speed was 4 ms for addition/subtraction, 8 ms for multiplication and 160 ms for division. The magnetic drum had a rotation speed of 5,600 rpm and a memory capacity of 1,024 words, and employed an original addressing scheme developed by Hitachi.

HIPAC MK-1 was co-developed by Hitachi, Ltd. and Hitachi Cable, Ltd. Used in the design of sags and tensions in transmission lines, it enabled the calculations for one segment to be conducted in approximately one minute whereas it would take approximately 7 hours by manual calculation. In 1958, HIPAC101 with twice the clock frequency and different word length was developed, and exhibited the following year at a UNESCO sponsored exhibition in Paris. Based on this, HIPAC101 was commercialized, and shipped from 1960, sold mainly for scientific technological computation. The HIPAC MK-1 played an important role in establishing the foundations of the domestic computer industry.

HIPAC MK-1 was designed with reference to the EDSAC built by the University of Cambridge and the ILLIAC built by the University of Illinois. Approximately 4000 parametron devices were used in HIPAC MK-1, and with a clock frequency of 10 kHz, calculation speed was 4 ms for addition/subtraction, 8 ms for multiplication and 160 ms for division. The magnetic drum had a rotation speed of 5,600 rpm and a memory capacity of 1,024 words, and employed an original addressing scheme developed by Hitachi.

HIPAC MK-1 was co-developed by Hitachi, Ltd. and Hitachi Cable, Ltd. Used in the design of sags and tensions in transmission lines, it enabled the calculations for one segment to be conducted in approximately one minute whereas it would take approximately 7 hours by manual calculation. In 1958, HIPAC101 with twice the clock frequency and different word length was developed, and exhibited the following year at a UNESCO sponsored exhibition in Paris. Based on this, HIPAC101 was commercialized, and shipped from 1960, sold mainly for scientific technological computation. The HIPAC MK-1 played an important role in establishing the foundations of the domestic computer industry.